# **R820T2 Register Description**

Rafael Suite 808, Building 53, No.195, Sec.4, Chung Hsing Road, Chutung, HsinChu 310, Taiwan, R.O.C. 310 台灣新竹縣竹東鎮中興路四段 195 號 53 館 808 室

Fax: 886-3-5820968

www.rafaelmicro.com

© 2011 by Rafael Microelectronics, Inc. All rights reserved.

# **1** Programming and Registers

# 1.1 I2C Series Programming Interface

The programmable features of the R820T2 are accessible through an I2C compatible serial interface. Bi-directional data transfers are programmed through the serial clock (SCL) and serial data lines (SDA) at a standard clock rate of 100 KHz and up to 400KHz.

## Data Transfer Logic

The  $I^2C$  control byte includes a fixed 7-bit slave address ID and a read/write (R/W) bit. Fixed  $I^2C$  slave address ID 0011010 (0x1A) is used for default setting. The R/W bit is set 0 for write and 1 for read (Table 1-1). Write mode and read mode will be further explained in the following sections.

# I<sup>2</sup>C Write/Read Address

# Table 1-1 : I<sup>2</sup>C Read / Write Address

| I <sup>2</sup> C Mode |     | I <sup>2</sup> C Address(Bin) |   |   |   |   |   |     | Address (Hex) |

|-----------------------|-----|-------------------------------|---|---|---|---|---|-----|---------------|

|                       | MSB |                               |   |   |   |   |   | LSB |               |

| Write Mode            | 0   | 0                             | 1 | 1 | 0 | 1 | 0 | 0   | 0x34          |

| Read Mode             | 0   | 0                             | 1 | 1 | 0 | 1 | 0 | 1   | 0x35          |

## Write Mode

When the slave address matches the  $I^2C$  device ID with write control bit ,  $I^2C$  start interprets the following first byte as first written register address. These following bytes are all the register data (page write  $I^2C$  control). Register 0 to Register 4 are reserved for internal use only and can be written by  $I^2C$  write command.

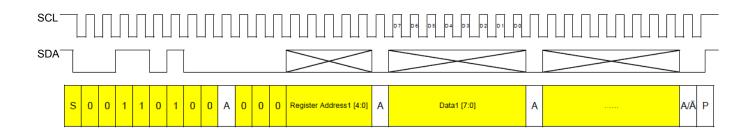

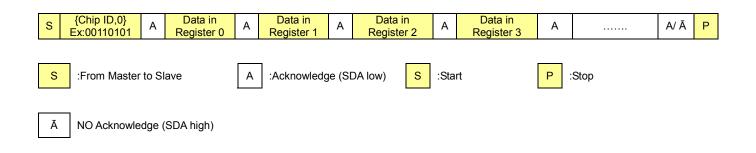

## Figure 1-1 : The Typical Write Mode Sequence

| S |                       | Address A | Data<br>(Reg. Address) | А     | Data<br>(Reg. Address+1) | А | Data<br>(Reg. Address+2) | А | <br>A/Ā | Ρ |

|---|-----------------------|-----------|------------------------|-------|--------------------------|---|--------------------------|---|---------|---|

| S | :From Master to Slave | e A       | :Acknowledge (SDA I    | 0\W() | S :Start                 |   | P :Stop                  |   |         |   |

| 3 |                       |           | Acknowledge (SDA I     | 000)  | .Start                   |   | - Stop                   |   |         |   |

| Ā | NO Acknowledge (SD    | )A high)  |                        |       |                          |   |                          |   |         |   |

# Figure 1-2 : An Example of Write Mode Procedure

## **Read Mode**

When the slave address matches the I<sup>2</sup>C device ID with read control bit, data are immediately transferred after ack command. Reading data transmission begins from core register 0 to final register until "P"(STOP) occurs. The data is transmitted from LSB to MSB, and the data of register 0 (0x96) is fixed as reference check point for read mode.

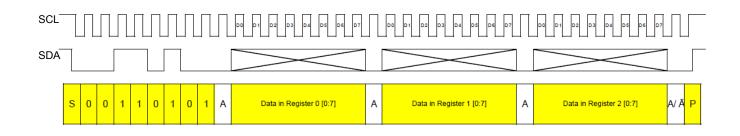

#### Figure 1-3 : The Typical Read Mode Sequence

### Figure 1-4 : An Example of Read Mode Procedure

# 1.2 Control Registers

# **Register Configuration**

Total 32 registers are programmable to set the major functions of R820T2. The register matrix in table 1-2 outlines the structure of register bit. Detail register description is listed in the next section:

# Table 1-2 : Register Matrix

| Reg<br>Address | Reg<br>Name | Write<br>/Read | В7         | B6                      | В5                 | B4              | B3            | B2         | B1              | B0    |  |

|----------------|-------------|----------------|------------|-------------------------|--------------------|-----------------|---------------|------------|-----------------|-------|--|

| 0x00           | R0          | R              | 1          | 0                       | 0                  | 1               | 0             | 1          | 1               | 0     |  |

| 0x01           | R1          | R              | -          | -                       | -                  | -               | -             | -          | -               | -     |  |

| 0x02           | R2          | R              | 0          |                         |                    | VCO_            | INDICATOR[    | 6:0]       |                 |       |  |

| 0x03           | R3          | R              |            |                         |                    | RF_INDICA       | .TOR [7:0]    |            |                 |       |  |

| 0x04           | R4          | R              | -          | -                       | -                  | -               | -             | -          | -               | -     |  |

| 0x05           | R5          | W/R            | PWD_LT     | 0                       | PWD_LNA1           | LNA_GAIN_MODE   | LNA_GAIN[3:0] |            |                 |       |  |

| 0x06           | R6          | W/R            | PWD_PDET1  | PWD_PDET3               | FILT_3DB           | 1               | 0             |            | PW_LNA[2:0]     |       |  |

| 0x07           | R7          | W/R            | 0          | PWD_MIX                 | PW0_MIX            | MIXGAIN_MODE    | MIX_GAIN[3:0] |            |                 |       |  |

| 0x08           | R8          | W/R            | PWD_AMP    | PW0_AMP                 | PW0_AMP IMR_G[5:0] |                 |               |            |                 |       |  |

| 0x09           | R9          | W/R            | PWD_IFFILT | r PW1_IFFILT IMR_P[5:0] |                    |                 |               |            |                 |       |  |

| 0x0A           | R10         | W/R            | PWD_FILT   | PW_F                    | FILT               | 1               |               | FILT_      | CODE[3:0]       |       |  |

| 0x0B           | R11         | W/R            | 0          | FILT_B                  | W[1:0]             | 0               | HPF[3:0]      |            |                 |       |  |

| 0x0C           | R12         | W/R            | 1          | PWD_VGA                 | 1                  | VGA_MODE        | VGA_CODE[3:0] |            |                 |       |  |

| 0x0D           | R13         | W/R            |            | LANV                    | TH_H[3:0]          |                 | LNAVTH_L[3:0] |            |                 |       |  |

| 0x0E           | R14         | W/R            |            | MIXV                    | TH_H[3:0]          |                 | MIXVTH_L[3:0] |            |                 |       |  |

| 0x0F           | R15         | W/R            | 0          | 0                       | 1                  | CLK_OUT_ENB     | 1             | 0          | CLK_AGC_ENB     | 0     |  |

| 0x10           | R16         | W/R            | :          | SEL_DIV[2:0]            |                    | REF_DIV2        | 0             | 1          | CAPX[           | 1:0]  |  |

| 0x11           | R17         | W/R            | PW_LD0     | D_A[1:0]                | 0                  | 0               | 0             | 0          | 1               | 1     |  |

| 0x12           | R18         | W/R            | 1          | 0                       | 0                  | 0               | PW_SDM        | 0          | 0               | 0     |  |

| 0x13           | R19         | W/R            | 0          | 0                       | 0                  | 0               | 0             | 0          | 0               | 0     |  |

| 0x14           | R20         | W/R            | S_120      | C[1:0]                  |                    |                 | N_12C[4:0]    |            |                 |       |  |

| 0x15           | R21         | W/R            |            |                         |                    | SDM_IN          | IN[8:1]       |            |                 |       |  |

| 0x16           | R22         | W/R            |            |                         |                    | SDM_IN          | [16:9]        |            |                 |       |  |

| 0x17           | R23         | W/R            | PW_LD0     | D_D[1:0]                | 1                  | 1               | OPEN_D        | 1          | 0               | 0     |  |

| 0x18           | R24         | W/R            | 0          | 1                       | -                  | -               | -             | -          | -               | -     |  |

| 0x19           | R25         | W/R            | PWD_RFFILT | 0                       | 0                  | SW_AGC          | 1             | 1          | -               | -     |  |

| 0x1A           | R26         | W/R            | RFMU       | IX[1:0]                 | 1                  | 0               | PLL_AUTO      | D_CLK[1:0] | RFFILT{         | [1:0] |  |

| 0x1B           | R27         | W/R            |            | TF_N                    | NCH[3:0]           |                 |               | TF         | _LP[3:0]        |       |  |

| 0x1C           | R28         | W/R            |            | PDET3                   | _GAIN[3:0]         |                 | 0             | 1          | -               | 0     |  |

| 0x1D           | R29         | W/R            | 1          | 1                       |                    | PDET1_GAIN[2:0] |               |            | PDET2_GAIN[2:0] |       |  |

| 0x1E           | R30         | W/R            | 0          | 1                       |                    |                 | PDET_C        | LK[4:0]    |                 |       |  |

| 0x1F           | R31         | W/R            | 1          | 1                       | 0                  | 0               | 0             | 0          | -               | -     |  |

# 1.3 Register Index and Description

| Reg  | R/W  | Bitmap | Symbol        | Description                                                 |

|------|------|--------|---------------|-------------------------------------------------------------|

|      | R/W  | [7]    | PWD_LT        | Loop through ON/OFF<br>0: on<br>1: off                      |

| R5   | R/W  | [5]    | PWD_LNA1      | LNA 1 power control<br>0:on<br>1:off                        |

| 0x05 | 0x05 | [4]    | LNA_GAIN_MODE | LNA gain mode switch<br>0: auto<br>1: manual                |

|      | R/W  | [3:0]  | LNA_GAIN[3:0] | LNA manual gain control<br>15: max gain<br>:<br>0: min gain |

|      | R/W  | [7]    | PWD_PDET1     | Power detector 1 on/off<br>0: on<br>1: off                  |

| R6   | R/W  | [6]    | PWD_PDET3     | Power detector 3 on/off<br>0: off<br>1: on                  |

| 0x06 | R/W  | [5]    | FILT_3DB      | Filter gain 3db<br>0:0db<br>1:+3db                          |

|      | R/W  | [2:0]  | PW_LNA[2:0]   | LNA power control<br>000: max<br>:<br>111: min              |

|      | R/W  | [6]    | PWD_MIX       | Mixer power<br>0:off<br>1:on                                |

| R7   | R/W  | [5]    | PW0_MIX       | Mixer current control<br>0:max current<br>1:normal current  |

| 0x07 | R/W  | [4]    | MIXGAIN_MODE  | Mixer gain mode<br>0:manual mode<br>1:auto mode             |

|      | R/W  | [3:0]  | MIX_GAIN[3:0] | Mixer manual gain control<br>0000->min<br>1111->max         |

| Reg   | R/W     | Bitmap     | Symbol         | Description                       |

|-------|---------|------------|----------------|-----------------------------------|

|       |         |            |                | Mixer buffer power on/off         |

|       | R/W     | [7]        | PWD_AMP        | 0: off                            |

|       |         |            |                | 1:on                              |

| R8    |         |            |                | Mixer buffer current setting      |

| 0x08  | R/W     | [6]        | PW0_AMP        | 0: high current                   |

| 0,000 |         |            |                | 1: low current                    |

|       |         |            |                | Image Gain Adjustment             |

|       | R/W     | [5:0]      | IMR_G[5:0]     | 0: min                            |

|       |         |            |                | 63: max                           |

|       |         |            |                | IF Filter power on/off            |

|       | R/W [7] | PWD_IFFILT | 0: filter on   |                                   |

|       |         |            |                | 1: off                            |

| R9    |         | [6]        |                | IF Filter current                 |

| 0x09  | R/W     |            | PW1_IFFILT     | 0: high current                   |

| 0209  | 0209    |            |                | 1: low current                    |

|       |         | [5:0]      |                | Image Phase Adjustment            |

|       | R/W     |            | IMR_P[5:0]     | 0: min                            |

|       |         |            |                | 63: max                           |

|       |         |            |                | Filter power on/off               |

|       | R/W     | [7]        | PWD_FILT       | 0: channel filter off             |

|       |         |            |                | 1: on                             |

|       |         |            |                | Filter power control              |

| R10   | R/W     | [6:5]      | PW_FILT[1:0]   | 00: highest power                 |

| 0x0A  |         |            |                | 11: lowest power                  |

|       |         |            |                | Filter bandwidth manual fine tune |

|       | R/W     | [3:0]      |                | 0000 Widest                       |

|       |         | [3.0]      | FILT_CODE[3:0] |                                   |

|       |         |            |                | 1111 narrowest                    |

| Reg  | R/W | Bitmap | Symbol         | Description                                           |  |  |  |

|------|-----|--------|----------------|-------------------------------------------------------|--|--|--|

|      |     |        |                | Filter bandwidth manual course tunnel                 |  |  |  |

|      |     | 10.51  | FILT_BW        | 00: widest                                            |  |  |  |

| R11  | R/W | [6:5]  |                | 10 or 01: middle                                      |  |  |  |

| 0x0B |     |        |                | 11: narrowest                                         |  |  |  |

|      |     |        |                | High pass filter corner control                       |  |  |  |

|      | R/W | [3:0]  | HPF[3:0]       | 0000: highest                                         |  |  |  |

|      |     |        |                | 1111: lowest                                          |  |  |  |

|      |     |        |                | VGA power control                                     |  |  |  |

|      | R/W | [6]    | PWD_VGA        | 0: vga power off                                      |  |  |  |

|      |     |        |                | 1: vga power on                                       |  |  |  |

| R12  |     | [4]    |                | VGA GAIN manual / pin selector                        |  |  |  |

| 0x0C | R/W |        | VGA_MODE       | 1: IF vga gain controlled by vagc pin                 |  |  |  |

| 0,00 |     |        |                | 0: IF vga gain controlled by vga_code[5:0]            |  |  |  |

|      | R/W | [3:0]  |                | IF vga manual gain control                            |  |  |  |

|      |     |        | VGA_CODE[3:0]  | 0000: -12.0 dB                                        |  |  |  |

|      |     |        |                | 1111: +40.5 dB; -3.5dB/step                           |  |  |  |

|      | R/W | [7:4]  |                | LNA agc power detector voltage threshold high setting |  |  |  |

|      |     |        | LNA_VTHH[4:0]  | 1111: 1.94 V                                          |  |  |  |

| R13  |     |        |                | 0000: 0.34 V, ~0.1 V/step                             |  |  |  |

| 0x0D |     |        |                | LNA agc power detector voltage threshold low setting  |  |  |  |

|      | R/W | [3:0]  | LNA_VTHL[3:0]  | 1111: 1.94 V                                          |  |  |  |

|      |     |        |                | 0000: 0.34 V, ~0.1 V/step                             |  |  |  |

|      |     |        |                | MIXER agc power detector voltage threshold high       |  |  |  |

|      | R/W | [7:4]  | MIX_VTH_H[4:0] | setting                                               |  |  |  |

|      |     |        |                | 1111: 1.94 V                                          |  |  |  |

| R14  |     |        |                | 0000: 0.34 V, ~0.1 V/step                             |  |  |  |

| 0x0E |     |        |                | MIXER agc power detector voltage threshold low        |  |  |  |

|      | R/W | [3:0]  | MIX_VTH_L[3:0] | setting                                               |  |  |  |

|      |     | [0.0]  |                | 1111: 1.94 V                                          |  |  |  |

|      |     |        |                | 0000: 0.34 V, ~0.1 V/step                             |  |  |  |

| R15<br>0x0F<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W | [4]<br>[1]<br>[7:5] | CLK_OUT_ENB   | Clock out pin control<br>0: clk output on<br>1: off<br>AGC clk control<br>0: internal agc clock on<br>1: off<br>PLL to Mixer divider number control |  |  |

|------------------------------------------------|---------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R15   0x0F   R/W   R/W   R16   0x10            | [1]                 | CLK_AGC_ENB   | 1: off   AGC clk control   0: internal agc clock on   1: off   PLL to Mixer divider number control                                                  |  |  |

| 0x0F<br>R/W<br>R/W<br>R/W<br>0x10              |                     |               | AGC clk control<br>0: internal agc clock on<br>1: off<br>PLL to Mixer divider number control                                                        |  |  |

| R/W<br>R/W<br>R/W<br>0x10                      |                     |               | 0: internal agc clock on<br>1: off<br>PLL to Mixer divider number control                                                                           |  |  |

| R/W<br>R/W<br>0x10                             |                     |               | 1: off<br>PLL to Mixer divider number control                                                                                                       |  |  |

| R16<br>0x10                                    | [7:5]               |               | PLL to Mixer divider number control                                                                                                                 |  |  |

| R16<br>0x10                                    | [7:5]               |               |                                                                                                                                                     |  |  |

| R16<br>0x10                                    | [7:5]               |               |                                                                                                                                                     |  |  |

| R16<br>0x10                                    | [7:5]               |               | 000: mixer in = vco out /2                                                                                                                          |  |  |

| 0x10                                           |                     | SEL_DIV[3:0]  | 001:mixer in = vco out / 4                                                                                                                          |  |  |

| 0x10                                           |                     |               | 010: mixer in = vco out / 8                                                                                                                         |  |  |

| 0x10                                           | -                   |               | 011:mixer in = vco out                                                                                                                              |  |  |

| 0x10                                           |                     | REFDIV        | PLL Reference frequency Divider                                                                                                                     |  |  |

|                                                | R/W [4]             |               | 0 -> fref=xtal_freq                                                                                                                                 |  |  |

| R/W                                            |                     |               | 1 -> fref=xta_freql / 2 (for Xtal >24MHz)                                                                                                           |  |  |

| R/W                                            |                     |               | Internal xtal cap setting                                                                                                                           |  |  |

| R/W                                            |                     | CAPX[1:0]     | 00->no cap ;                                                                                                                                        |  |  |

|                                                | [1:0]               |               | 01->10pF                                                                                                                                            |  |  |

|                                                |                     |               | 10->20pF ;                                                                                                                                          |  |  |

|                                                |                     |               | 11->30pF                                                                                                                                            |  |  |

|                                                |                     |               | PLL analog low drop out regulator switch                                                                                                            |  |  |

| R17                                            |                     |               | 00: off                                                                                                                                             |  |  |

| 0x11 R/W                                       | [7:6]               | PW_LDO_A[1:0] | 01: 2.1V                                                                                                                                            |  |  |

| UX II                                          |                     |               | 10: 2.0V                                                                                                                                            |  |  |

|                                                |                     |               | 11: 1.9V                                                                                                                                            |  |  |

|                                                |                     |               | PLL integer divider number input Si2c                                                                                                               |  |  |

| <b>R20</b> R/W                                 | [7:6]               | SI2C[1:0]     | Nint=4*Ni2c+Si2c+13                                                                                                                                 |  |  |

| 0x14                                           |                     |               | PLL divider number Ndiv = (Nint + Nfra)*2                                                                                                           |  |  |

| R/W                                            | [5:0]               | NI2C[5:0]     | PLL integer divider number input Ni2c                                                                                                               |  |  |

| R21                                            | [7:0]               | SDM_IN[7:0]   | PLL fractional divider number input SDM[16:1]                                                                                                       |  |  |

| 0x15                                           | []                  | (1.00)        | Nfra=SDM IN[16]*2^-1+SDM IN[15]*2^-2++SDM IN[2]                                                                                                     |  |  |

| R22<br>0x16                                    |                     | SDM_IN[7:0]   | *2^-15+SDM_IN[1]*2^-16                                                                                                                              |  |  |

| Reg  | R/W      | Bitmap         | Symbol          | Description                                                |

|------|----------|----------------|-----------------|------------------------------------------------------------|

|      |          |                |                 | PLL digital low drop out regulator supply current switch   |

|      |          |                |                 | 00: 1.8V,8mA                                               |

|      | R/W      | [7:6]          | PW_LDO_D[1:0]   | 01: 1.8V,4mA                                               |

| R23  |          |                |                 | 10: 2.0V,8mA                                               |

| 0x17 |          |                |                 | 11: OFF                                                    |

|      |          |                |                 | Open drain                                                 |

|      | R/W      | [3]            | OPEN_D[3]       | 0: High-Z                                                  |

|      |          |                |                 | 1: Low-Z                                                   |

|      |          |                |                 | RF Filter power                                            |

|      | R/W      | [7]            | PWD_RFFILT      | 0: off                                                     |

| R25  |          |                |                 | 1:on                                                       |

| 0x19 |          | [4]            | SW_AGC          | Switch agc_pin                                             |

|      | R/W      |                |                 | 0:agc=agc_in                                               |

|      |          |                |                 | 1:agc=agc_in2                                              |

|      | R/W      | [7:6]          |                 | Tracking Filter switch                                     |

|      |          |                | RFMUX[1:0]      | 00: TF on                                                  |

|      |          |                |                 | 01: Bypass                                                 |

|      |          |                |                 | PLL auto tune clock rate                                   |

| R26  | R/W      | [3:2]          | PLL_AUTO_CLK[1  | 00: 128 kHz                                                |

| 0x1A |          | [3.2]          | :0]             | 01: 32 kHz                                                 |

|      |          |                |                 | 10: 8 kHz                                                  |

|      |          |                |                 | RF FILTER band selection                                   |

|      | R/W      | [1:0]          | RFFILT[1:0]     | 00: highest band                                           |

|      |          | [1:0]          |                 | 01:med band                                                |

|      |          |                |                 | 10:low band                                                |

| R27  | R/W      | [7:4]          | TF_NCH[1:0]     | 0000 highest corner for LPNF; 1111 lowerst corner for LPNF |

| 0x1B | R/W      | [3:0]          | TF_LP[3:0]      | 0000 highest corner for LPF; 1111 lowerst corner for LPF   |

|      |          |                |                 | Power detector 3 TOP(take off point) control               |

| R28  | R/W      | [ <b>7</b> ·41 | PDET3_GAIN[1:0] | 0: Highest                                                 |

| 0x1C | F\$/ V V | [7:4]          |                 | :                                                          |

|      |          |                |                 | 15: Lowest                                                 |

| Reg  | R/W | Bitmap | Symbol          | Description                                                                   |

|------|-----|--------|-----------------|-------------------------------------------------------------------------------|

| R29  | R/W | [5:3]  | PDET1_GAIN[2:0] | Power detector 1 TOP(take off point) control<br>0: Highest<br>:<br>15: Lowest |

| 0x1D | R/W | [2:0]  | PDET2_GAIN[2:0] | Power detector 2 TOP(take off point) control<br>0: Lowest<br>:<br>7: Highest  |

| R30  | R/W | [5:0]  | PDET_CLK[5:0]   | Power detector timing control<br>111111: max<br>:<br>000000: min              |

| 0x1E | R/W | [6]    | FILTER_EXT      | Filter extension under weak signal<br>0: Disable<br>1: Enable                 |